多亏了物理定律和摩尔定律,我们只能在一个设备中装入这么多的硅。挑战一直是在不增加空间量的情况下塞满尽可能多的组件。除了改进制造工艺之外,解决这个难题的关键之一是想出创造性的方法来完成旧的技术和设计。这就是三星在其新的 DRAM 技术中所吹嘘的,该技术通过抛弃传统的 TSV 引线键合技术,能够在与 8 个芯片相同的空间中堆叠 12 个 DRAM 芯片。

由于空间限制,硅制造商已经走向三维。当你不能水平扩展时,你尝试垂直扩展。使用引线键合通常可以堆叠芯片,但这些引线虽然很细,但仍然占据芯片层之间的空间。

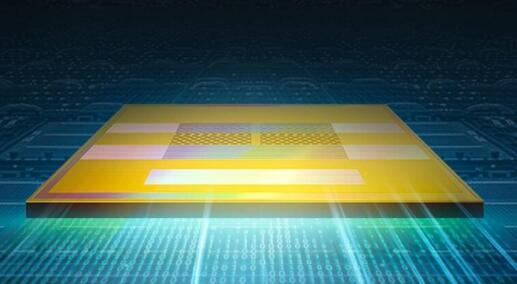

相比之下,正如技术名称所暗示的那样,3D 硅通孔或 TSV 将连接器穿过芯片。它不仅在水平方向上占用的空间更少,而且还减少了每层硅之间的填充。此外,它甚至减少了整体材料的使用,因为芯片和下方 PCB 之间的连接也更短。

尽管有很多好处,但 TSV 技术实际上更难实现,而且也更昂贵。事实上,三星的公告显示它使用了不少于 60,000 个孔来实现这一目标。然而,同样令人印象深刻的是,它如何设法使用该技术将 12 个 DRAM 芯片堆叠在与之前的 8 层引线键合 DRAM 解决方案相同的高度,后者只有 720 ㎛(微米)高。

最重要的是,它可以在与当前产品相同的空间内提供更高容量的 DRAM 产品。具体来说,三星计划通过这种 12 层 3D TSV 技术生产 24 GB DRAM。然而,这是针对其高带宽内存 2 (HBM2) 系列,这暗示了它的价格和稀有性,即使对于企业客户也是如此。